Input Capture

The Scamp processor has six input capture (IC) modules, labelled IC1 through IC6, that can be used for capturing input pulse events. Each module operates independently with a 16-bit timer. For 32-bit resolution, two modules can be paired together if required. Input capture works by capturing the timer value when a transition on an IC input occurs. It can be configured for any transition, or every rising-edge transition, or every 4th or 16th rising-edge transition.

To configure an input capture, the first step is to assign an IC module to an input pin using Peripheral Pin Select (PPS). See the page on Peripheral Pin Select for an overview of this process. So, as an example, let's say we will use IC1 and connect it to pin 2 of the Scamp. Pin 2 corresponds to RP2. The pin allocation for the IC1 module is controlled by register RPINR7 at address $039a. Therefore, we need to write the value (decimal) 2 to the lower half of RPINR7.

#2 $39a c!

IC1 is now connected to pin 2.

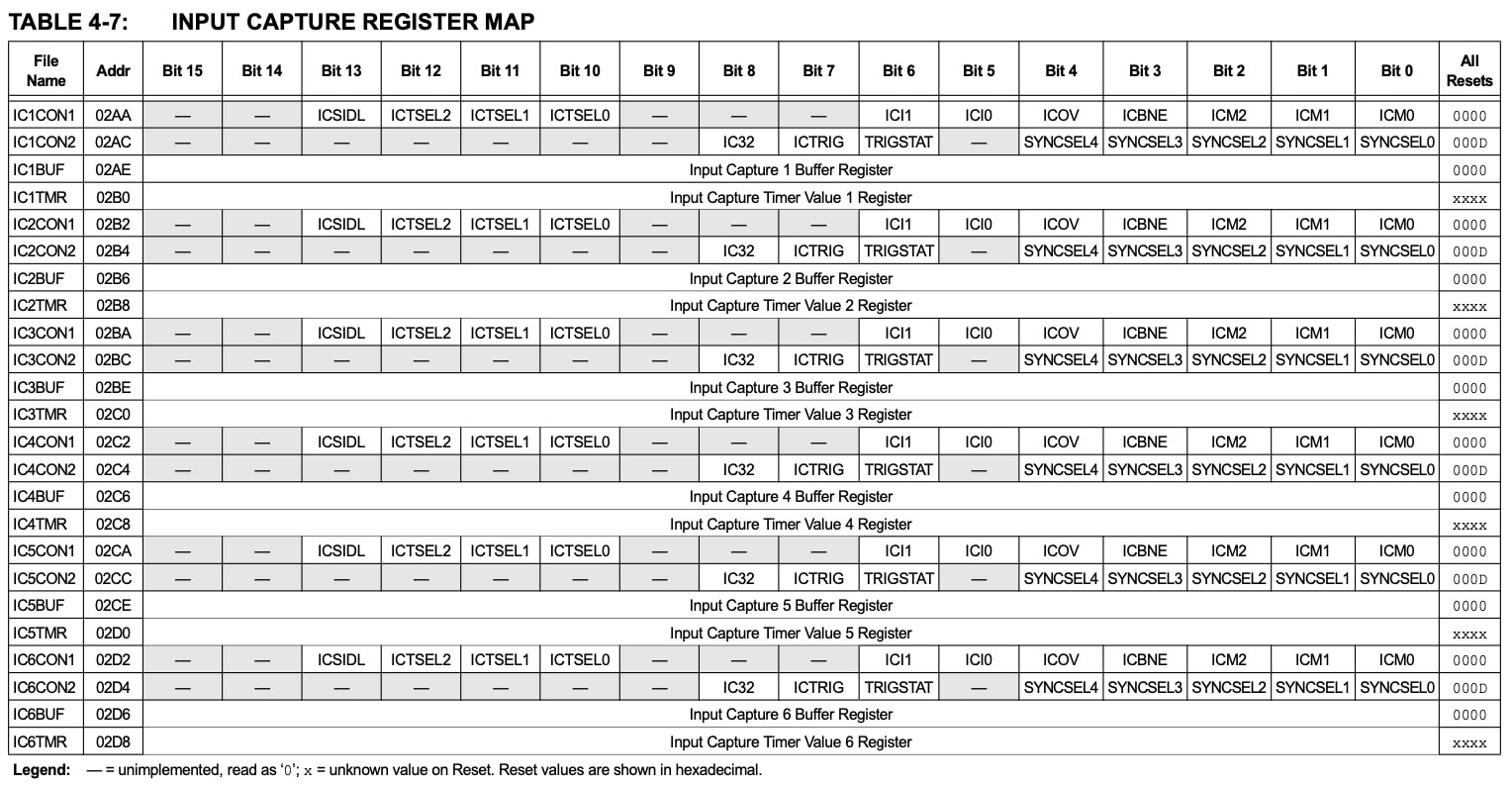

The registers to configure, control and read the IC modules are shown in Table 4-7 from the processor's datasheet.

The registers to configure, control and read the IC modules are shown in Table 4-7 from the processor's datasheet.

Understanding the Control Registers

ICxCON1 and ICxCON2 are the control registers for each of the modules. Note that not all bits in the register are used.

In ICxCON1, bit ICSIDL selects whether the input capture module halts when the processor is idle (bit = 1), or whether the modules continues to operate when the processor is idle (bit = 0).

The three ICTSEL bits configure the timer source for the module. If the bits are 111 then the source is the system clock, while 100 selects Timer 1, 011 selects Timer 5, 010 selects Timer 4, 001 selects Timer 2 and 000 selects Timer 3. The default at reset is Timer 3.

The two bits ICI select the number of captures per interrupt. 00 captures on every event, 01 captures on every second event, 10 captures on every third event, and 11 captures on every fourth event.

ICOV is a (read only) status bit indicating whether an overflow has occurred.

ICBNE is a (read only) status bit showing whether the buffer is empty (0) or not empty (1).

And finally, the three ICM bits control the Input Capture Mode. 000 turns the module off, 001 selects that the module will capture on every rising and falling edge. 010 captures on every falling edge. 011 captures on every rising edge. 100 captures on every fourth rising edge. 101 captures on every 16th rising edge. 110 is unused, and 111 selects for the IC module to generate an interrupt only when the processor is idle or asleep. This can be used to wake the processor from sleep when an external event has occurred.

In ICxCON2, the bit IC32 selects either 16 bit operation (bit = 0) or cascades two modules together for 32-bit operation (bit = 1). For 32-bit operation, IC32 must be set in both modules.

ICTRIG controls whether the module is synchronised (bit = 0) with the source designated by the SYNCSEL bits, or triggered by the source (bit = 1). The TRIGSTAT bit indicates whether the timer source has been triggered and running (bit = 1) or is not triggered (bit = 0).

The SYNCSEL bits specify the source of the synchronization/trigger. Valid bits configurations are:

In ICxCON1, bit ICSIDL selects whether the input capture module halts when the processor is idle (bit = 1), or whether the modules continues to operate when the processor is idle (bit = 0).

The three ICTSEL bits configure the timer source for the module. If the bits are 111 then the source is the system clock, while 100 selects Timer 1, 011 selects Timer 5, 010 selects Timer 4, 001 selects Timer 2 and 000 selects Timer 3. The default at reset is Timer 3.

The two bits ICI select the number of captures per interrupt. 00 captures on every event, 01 captures on every second event, 10 captures on every third event, and 11 captures on every fourth event.

ICOV is a (read only) status bit indicating whether an overflow has occurred.

ICBNE is a (read only) status bit showing whether the buffer is empty (0) or not empty (1).

And finally, the three ICM bits control the Input Capture Mode. 000 turns the module off, 001 selects that the module will capture on every rising and falling edge. 010 captures on every falling edge. 011 captures on every rising edge. 100 captures on every fourth rising edge. 101 captures on every 16th rising edge. 110 is unused, and 111 selects for the IC module to generate an interrupt only when the processor is idle or asleep. This can be used to wake the processor from sleep when an external event has occurred.

In ICxCON2, the bit IC32 selects either 16 bit operation (bit = 0) or cascades two modules together for 32-bit operation (bit = 1). For 32-bit operation, IC32 must be set in both modules.

ICTRIG controls whether the module is synchronised (bit = 0) with the source designated by the SYNCSEL bits, or triggered by the source (bit = 1). The TRIGSTAT bit indicates whether the timer source has been triggered and running (bit = 1) or is not triggered (bit = 0).

The SYNCSEL bits specify the source of the synchronization/trigger. Valid bits configurations are:

- 11100 = CTMU

- 11011 = ADC

- 11010 = Comparator 3

- 11001 = Comparator 2

- 11000 = Comparator 1

- 10101 = IC6

- 10100 = IC5

- 10011 = IC4

- 10010 = IC3

- 10001 = IC2

- 10000 = IC1

- 01111 = Timer 5

- 01110 = Timer 4

- 01101 = Timer 3

- 01100 = Timer 2

- 01011 = Timer 1

- 00110 = Output Compare 6

- 00101 = Output Compare 5

- 00100 = Output Compare 4

- 00011 = Output Compare 3

- 00010 = Output Compare 2

- 00001 = Output Compare 1

- 00000 = No synchronisation with another module

Using Input Capture

For this example, let's configure IC1 to use pin 2. We configure control register 1 so that the module halts when the processor is idle, the system clock is selected as the source for the module, we capture an interrupt on every event, and we capture on every rising edge. (Note that not all bits in the register are used.) So the value for control register 1 is %0011110000000011. We will also configure it for 16-bit operation, with the module synchronised with the source and select the source to be no other module. The value for control register 2 is %000000000000000.

$02aa constant IC1CON1 \ define addresses of registers

$02ac constant IC1CON2

$02ae constant IC1BUF

$039a constant RPINR7

: IC1-init

#2 RPINR7 c! \ map IC1 to pin 2

%0011110000000011 IC1CON1 ! \ initialize control registers

0 IC1CON2 !

\ clear the buffer by reading IC1BUF

\ until ICBNE bit cleared

begin

IC1BUF @ drop

IC1CON1 @ %0000000000001000 and \ mask out unwanted bits

0= until

;

Run IC1-init to initialize the IC module.

To read the value from IC1:

To read the value from IC1:

IC1BUF @

Note that if there is no synchronization between your pulse source and your input capture, the values may appear random.

Learn : Interfacing :